台积电公布:汽车Chiplet,3nm新版本

台积电计划在 2025 年底前推出其 3D 结构小芯片技术的汽车级版本。

InFO-oS 扇出技术将支持基板上的多个 SoC 器件,第一个汽车小芯片工艺设计套件 (PDK) 将于今年年底推出,完整的 PDK 将于 2026 年初推出。

CoWoS-R 工艺将通过基板的中介层支持具有高性能 HBM 存储器的 SOC。初始 PDK 很快就会推出,完整的 PDK 也将于 2026 年初推出。台积电昨天在其欧洲技术研讨会上表示,这些工艺将于 25 年第 4 季度通过 AEC Q100 Grade2 认证。

CoWoS 平台包括最成熟的基于硅中介层的 CoWoS-S 和基于有机中介层的 CoWoS-L 和 R。汽车工艺建立在超过 150 个 CoWoS 客户产品流片的经验之上,截至本年底,已为超过 25 个客户提供服务。

汽车也是 ESMC 合资工厂的关键,该工厂将于今年晚些时候开始建设,并于 2027 年实现量产。ESMC 是博世、英飞凌、恩智浦和台积电的战略合作和承诺,旨在为欧洲客户提供 N28 和 N16 工艺技术。

性能优化的3nm有望量产

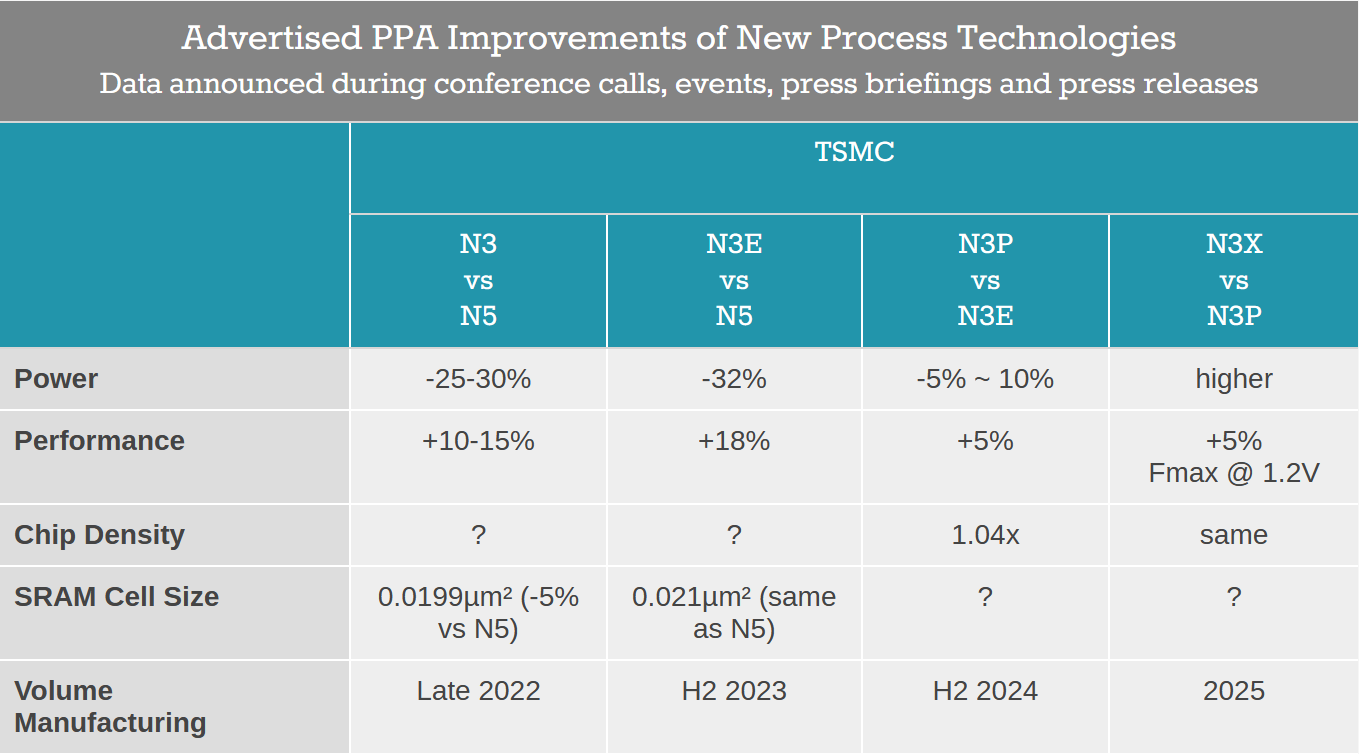

作为台积电春季技术研讨会系列第二站的一部分,该公司提供了有关其 3 纳米级工艺当前和未来状态的最新信息。在当前一代 N3E 工艺的基础上,该工艺技术的光学微缩技术 N3P 现已有望在 2024 年下半年进入量产。得益于这种微缩,N3P 预计将提供更高的性能与 N3E 相比,效率更高,晶体管密度更高。

随着 N3E 已经投入量产,台积电报告称,他们在第二代 3nm 级工艺说明上看到了“巨大”的良率。据该公司称,N3E 的 D0 缺陷密度与 N5 相当,与旧节点在其各自生命周期中同一点的缺陷率相匹配。考虑到开发最后一代、更精细的 FinFET 技术会带来额外的复杂性,这绝非易事。因此,对于台积电的尖端客户(例如刚刚推出 M4 SoC 的苹果公司)来说,这使他们能够相对较快地获得改进工艺节点的好处。

台积电一位高管在活动中表示:“N3E 按计划于去年第四季度开始量产。” “我们已经看到客户产品的出色产量表现,因此他们确实按计划进入了市场。”

台积电的N3E节点是N3B的宽松版本,消除了一些EUV层并完全避免了EUV双图案的使用。这使得生产成本更便宜,并且在某些情况下它扩大了工艺窗口和产量,尽管它是以一些晶体管密度为代价的。

同时,展望台积电的未来,N3P 已完成资格认证,其良率表现接近 N3E。作为光学微缩技术,N3P 节点将使处理器开发人员能够在相同漏电情况下将性能提高 4%,或者在相同时钟频率下将功耗降低 9%(之前范围在 4% 至 10% 之间,具体取决于设计) )。新节点还将“混合”芯片设计的晶体管密度提高 4%,台积电将其定义为由 50% 逻辑、30% SRAM 和 20% 模拟电路组成的处理器。

虽然看起来最初的 N3(又名 N3B)的生命周期相对平静,因为苹果是其唯一的主要客户,但 N3E 将被台积电的广泛客户采用,其中包括许多业界最大的芯片设计商。

由于 N3P 是 N3E 的光学微缩版,因此它在 IP 模块、工艺规则、电子设计自动化 (EDA) 工具和设计方法方面与其前身兼容。因此,台积电预计大部分新流片将使用 N3P,而不是 N3E 或 N3。这是合乎逻辑的,因为 N3P 以比 N3 更低的成本提供比 N3E 更高的性能效率。

N3P 最重要的一点是,它有望在今年下半年投入生产,因此预计芯片设计人员会立即采用它。

“我们还成功交付了 N3P 技术,”台积电高管表示。“它已经通过了认证,良率表现接近N3E。[工艺技术]也已收到产品客户流片,并将于今年下半年开始生产。由于N3P的[PPA优势],我们预计N3 上的大部分流片都流向了 N3P。”

原文链接:

https://www.anandtech.com/show/21394/tsmc-performanceoptimized-3nm-process-technology-on-track-for-mass-production-this-year

请先 登录后发表评论 ~