台积电技术路线图更新,详解

昨天,我们发布了台积电在北美技术峰会发布了新技术的新闻,具体参考《台积电发布1.6nm》。

今天外媒就当中一些技术深入解读。

2nm的一些变化

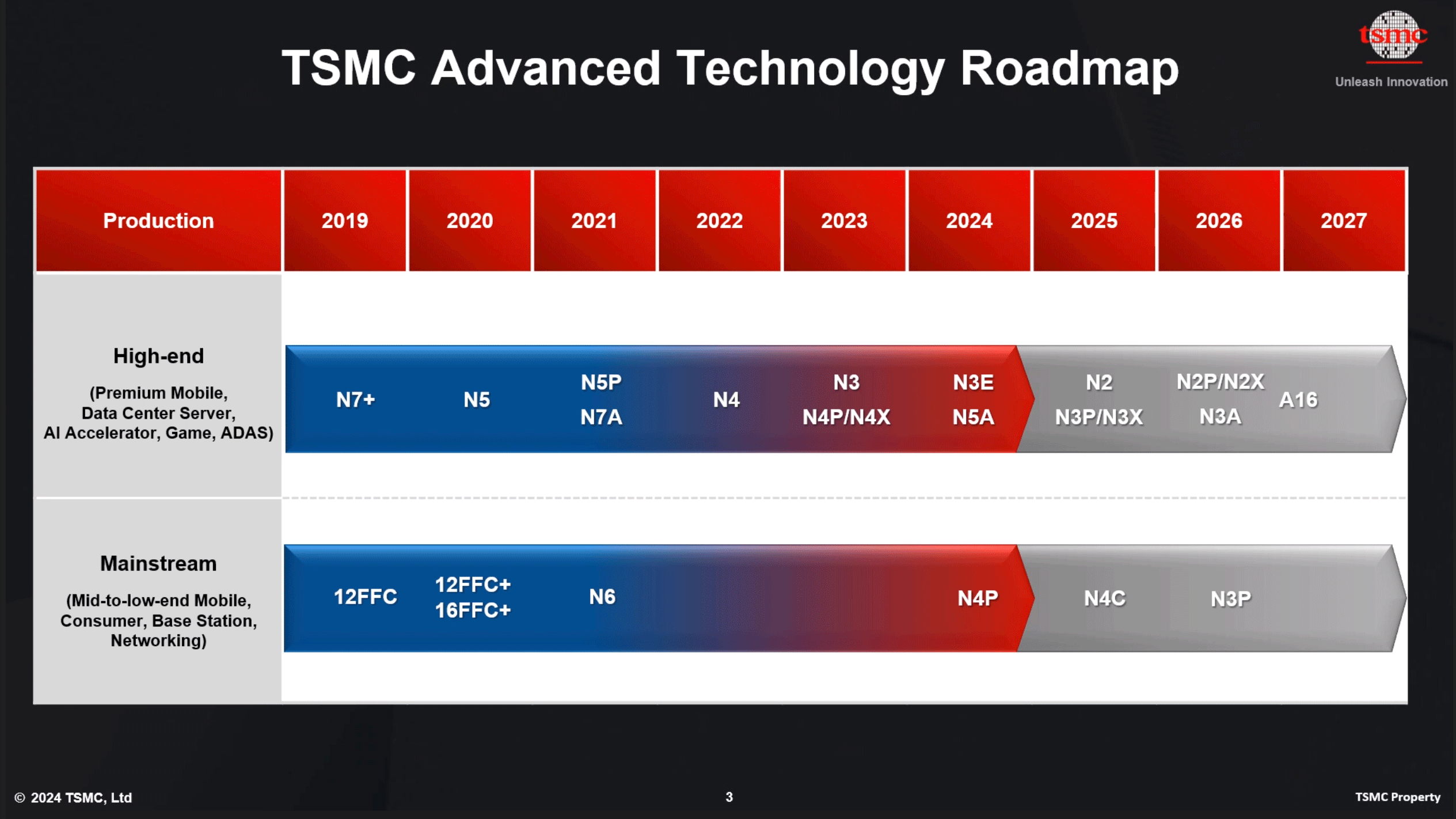

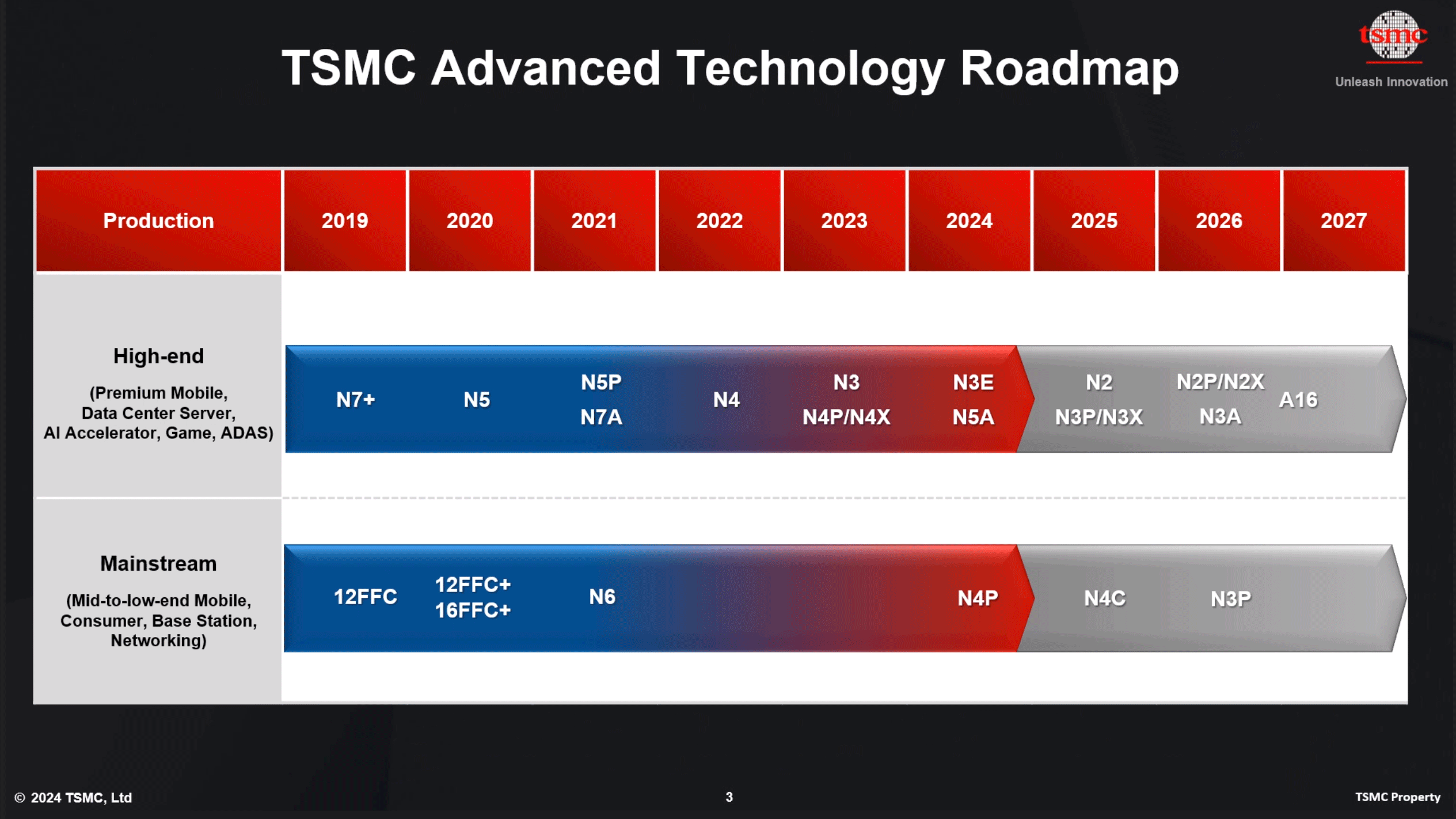

根据台积电规划,2025 年下半年开始在其第一代 GAAFET N2 节点上量产芯片,N2P 将在 2026 年末接替 N2——尽管没有先前宣布的背面供电功能。同时,整个 N2 系列将添加台积电的新 NanoFlex 功能,该功能允许芯片设计人员混合和匹配来自不同库的单元,以优化性能、功耗和面积 (PPA)。

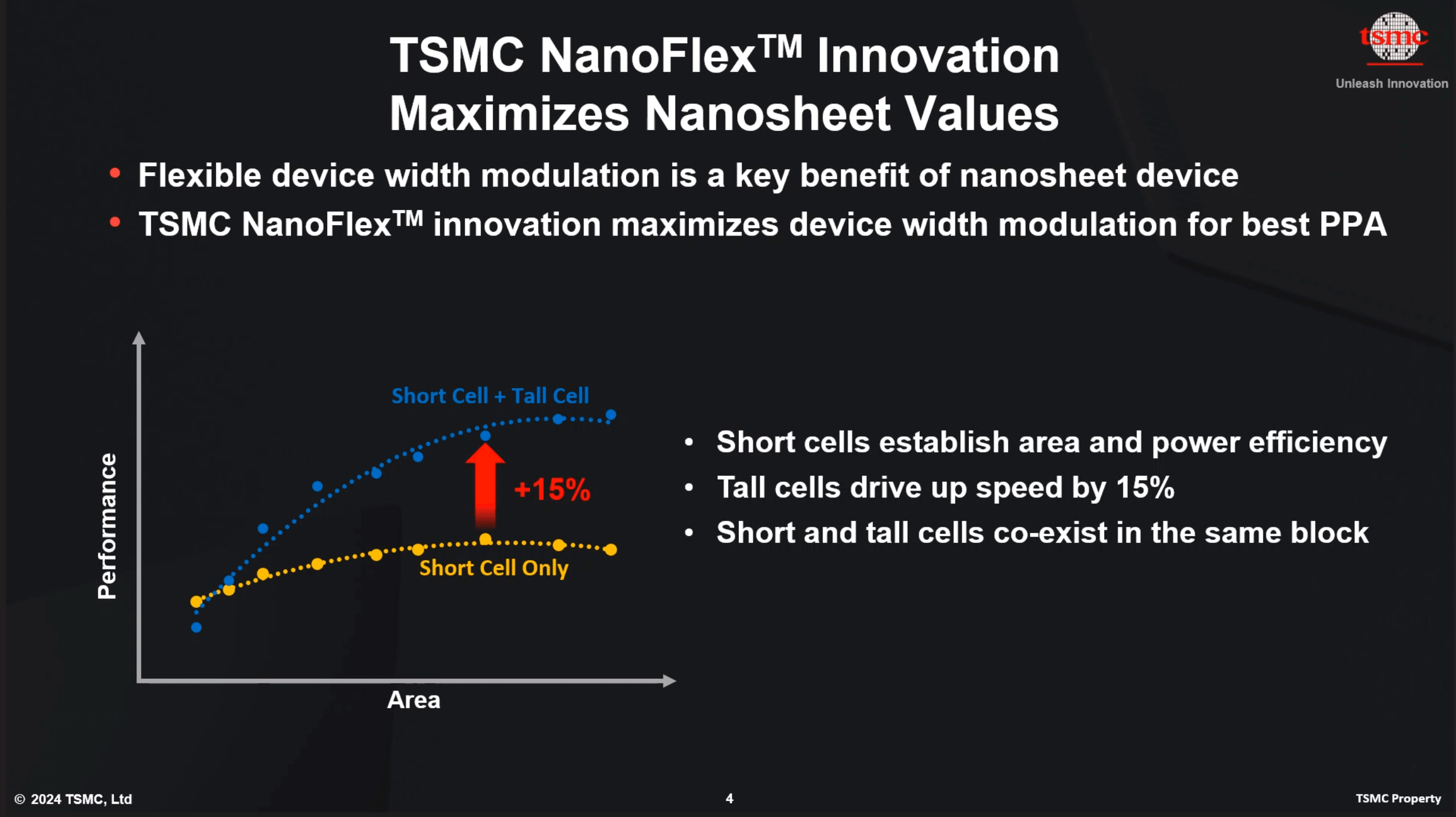

此次活动的重要公告之一是台积电的 NanoFlex 技术,该技术将成为该公司完整的 N2 系列生产节点(2 纳米级、N2、N2P、N2X)的一部分。NanoFlex将使芯片设计人员能够在同一块设计中混合和匹配来自不同库(高性能、低功耗、面积高效)的单元,从而使设计人员能够微调其芯片设计以提高性能或降低功耗。

台积电的当代 N3 制造工艺已经支持称为FinFlex的类似功能 ,该功能还允许设计人员使用来自不同库的单元。但由于 N2 依赖于环栅 (GAAFET) 纳米片晶体管,NanoFlex 为台积电提供了一些额外的控制:首先,台积电可以优化通道宽度以提高性能和功耗,然后构建短单元(为了面积和功率效率)或高单元(性能提升高达 15%)。

就时间安排而言,台积电的 N2 计划于 2025 年进入风险生产,并于 2025 年下半年进入大批量生产(HVM),因此看起来我们将在 2026 年在零售设备中看到 N2 芯片。与N3E相比,台积电预计N2在相同功耗下性能提升10%到15%,或者在相同频率和复杂度下功耗降低25%到30%。至于芯片密度,代工厂希望将密度提高 15%,按照当代标准,这是一个很好的扩展程度。

N2之后将是性能增强型N2P,以及2026年的电压增强型N2X。虽然台积电曾表示N2P将在2026年添加背面供电网络(BSPDN),但看起来情况不会如此,N2P将使用常规供电电路。原因尚不清楚,但看起来该公司决定不在 N2P 中添加昂贵的功能,而是将其保留到下一代节点,该节点也将于 2026 年末向客户提供。

N2预计仍将采用与电源相关的重大创新: 超高性能金属-绝缘体-金属(SHPMIM)电容器,其添加是为了提高电源稳定性。SHPMIM 电容器的容量密度是台积电现有超高密度金属-绝缘体-金属 (SHDMIM) 电容器的两倍以上。此外,与前代产品相比,新型 SHPMIM 电容器将方块电阻(Rs,单位为欧姆/平方)和通孔电阻 (Rc) 降低了 50%。

1.6nm,使用背面供电

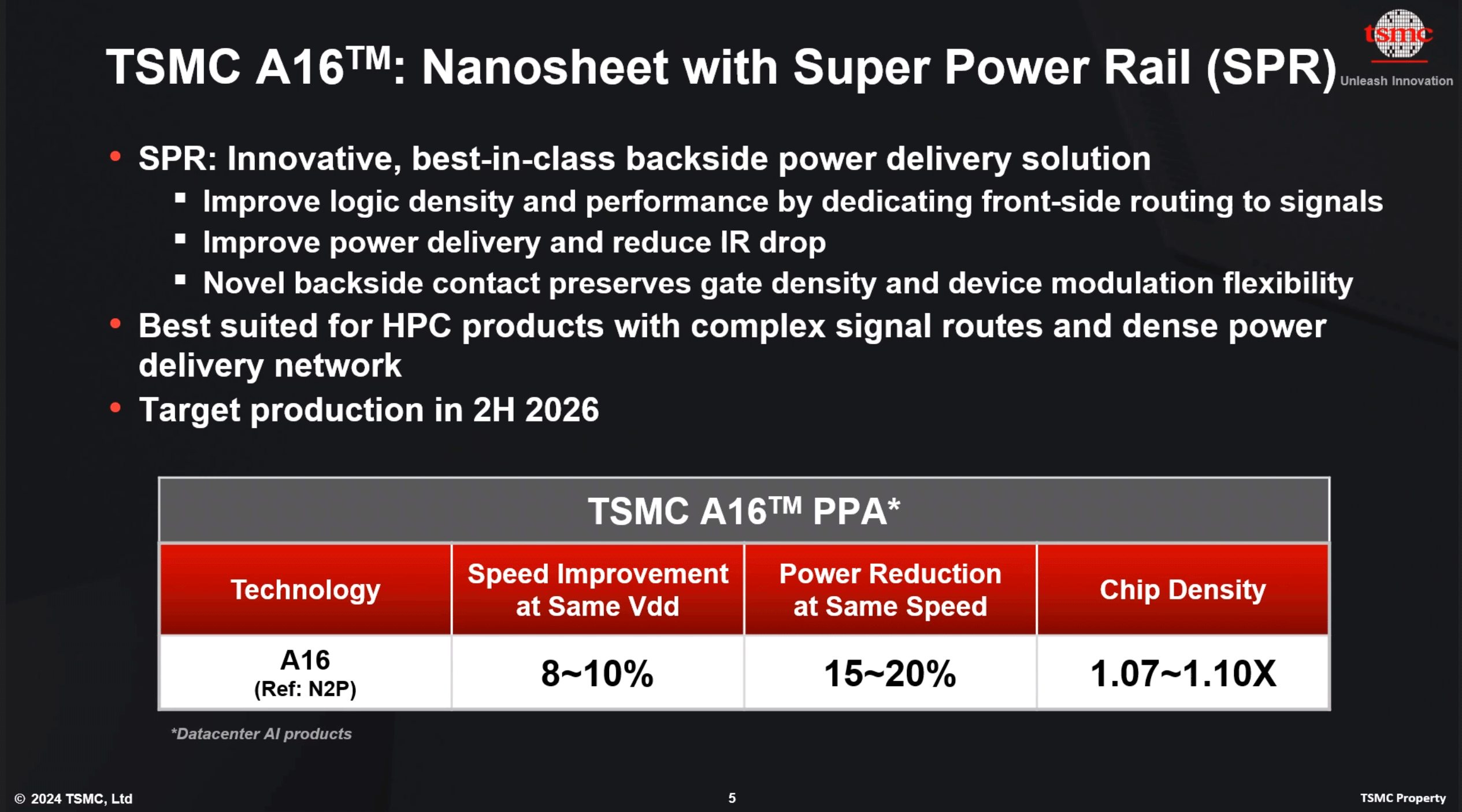

台积电在硅谷站的头条新闻中宣布了其首款“埃级”工艺技术:A16。在生产计划发生变化,从台积电的 N2P 节点中删除背面供电网络技术 (BSPDN) 后,新的 1.6 纳米级生产节点现在将成为将 BSPDN 引入台积电芯片制造系列的第一个工艺。与台积电的 N2P 制造工艺相比,通过增加背面供电功能和其他改进,台积电预计 A16 将提供显着改进的性能和能效。将从 2026 年下半年开始向台积电的客户提供。

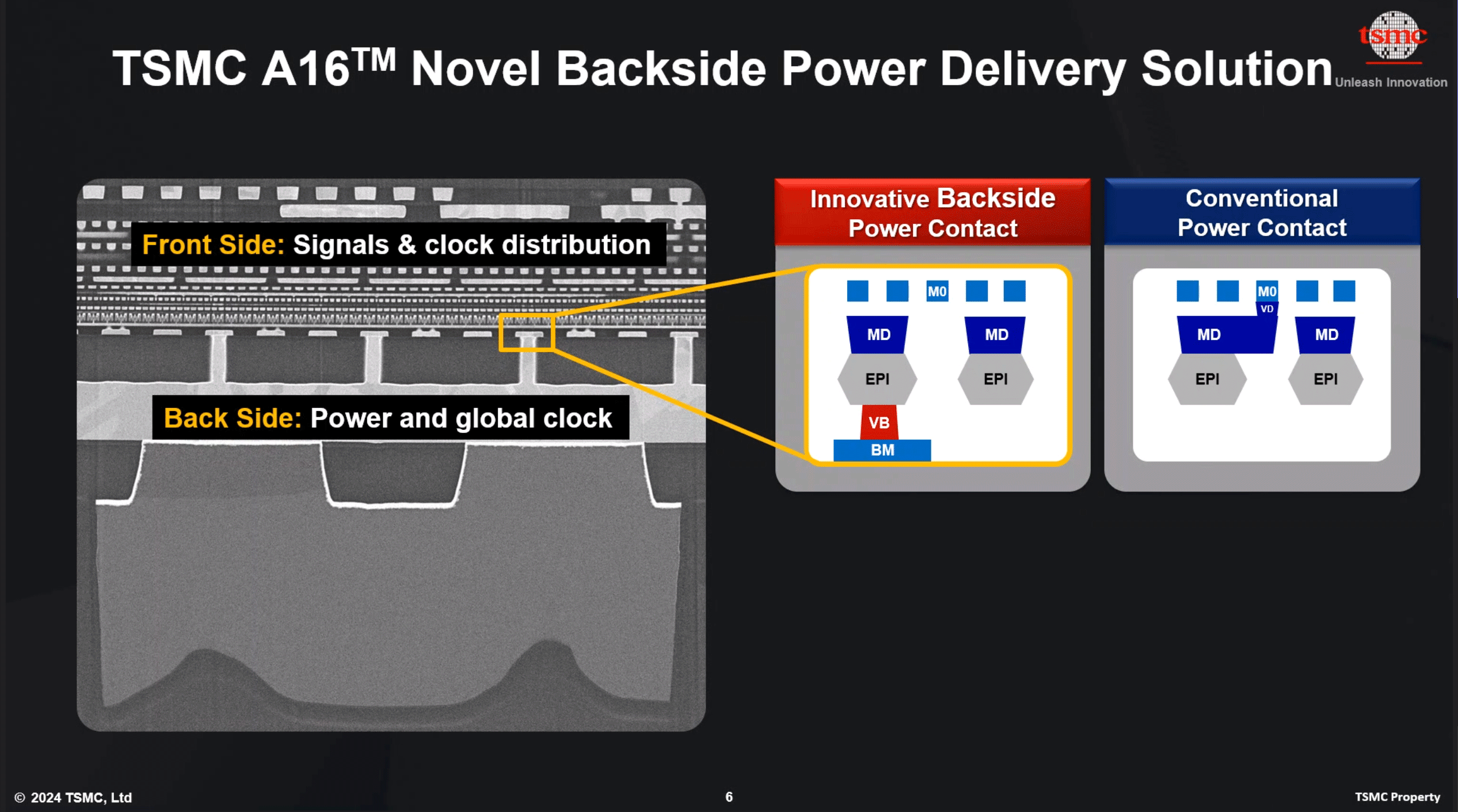

从高水平来看,台积电的 A16 工艺技术将依赖于环栅 (GAAFET) 纳米片晶体管,并将采用背面电源轨,这将改善功率传输并适度增加晶体管密度。与台积电的 N2P 制造工艺相比,A16 预计在相同电压和复杂度下性能提升 8% 至 10%,或者在相同频率和晶体管数量下功耗降低 15% 至 20%。台积电目前尚未列出详细的密度参数,但该公司表示芯片密度将增加 1.07 倍至 1.10 倍 - 请记住,晶体管密度在很大程度上取决于所使用的晶体管的类型和库。

台积电 A16 节点的关键创新是其超级电源轨 (SPR) 背面供电网络,这是台积电的首创。这家合约芯片制造商声称,A16 的 SPR 专为具有复杂信号路线和密集电源电路的高性能计算产品量身定制。

如前所述,随着本周的发布,A16 现已成为台积电背面供电的工具。该公司最初计划在 2026 年通过 N2P 提供 BSPDN 技术,但由于尚不完全清楚的原因,该技术已从 N2P 转移到 A16。台积电 2023 年 N2P 的官方时间安排总是有点宽松,因此很难说这是否代表了台积电 BSPDN 的实际延迟。但与此同时,需要强调的是,A16 不仅仅是 N2P 的更名,而且它将是与 N2P 不同的技术。

台积电并不是唯一一家追求背面电力传输的晶圆厂,因此,我们看到不同晶圆厂出现了该技术的多种变体。整个行业对于 BSPDN 有三种方法:Imec 的 Buried Power Rail、Intel 的 PowerVia 以及现在 TSMC 的 Super Power Rail。

最古老的技术是 Imec 的埋地电源轨,本质上是将电力传输网络放置在晶圆背面,然后使用纳米 TSV 将逻辑单元的电源轨连接到电源触点。这可以实现一定的面积缩放,并且不会给生产增加太多复杂性。第二种实现是英特尔的 PowerVia,将电源连接到单元或晶体管触点,这提供了更好的结果,但代价是复杂性。

最后,我们拥有台积电的新型超级电源轨 BSPDN 技术,该技术将背面电源网络直接连接到每个晶体管的源极和漏极。据台积电称,就面积缩放而言,这是最有效的技术,但代价是它在生产方面是最复杂(且昂贵)的。

TSMC 选择使用最复杂的 BSPDN 版本可能是我们看到它从 N2P 中删除的部分原因,因为实施它最终会增加时间和成本。这使得 A16 成为台积电在 2026/2027 年时间范围内的首要性能节点,而 N2P 可以提供更平衡的性能和成本效率组合。

最后,与英特尔一样,我们也看到台积电从这一代技术开始采用新的工艺节点命名约定。名称本身在很大程度上是任意的——这种情况在晶圆厂行业已经存在好几年了——但由于当前的节点名称已经是个位数(例如 N2),该行业需要将节点名称重新校准为某种名称。小于纳米。因此,我们已经到达了“埃时代”。但无论它到底叫什么或者为什么这么叫,重要的一点是A16将是超越台积电2nm级产品的下一代节点。

台积电预计 A16 将于 2026 年下半年开始量产,因此基于该技术的首批产品很可能会在 2027 年上市。鉴于时间安排,该生产节点可能会与英特尔的 14A竞争;尽管两年多后,目前还没有人批量生产 BSPDN,但计划和路线图仍然有很多时间可以改变。

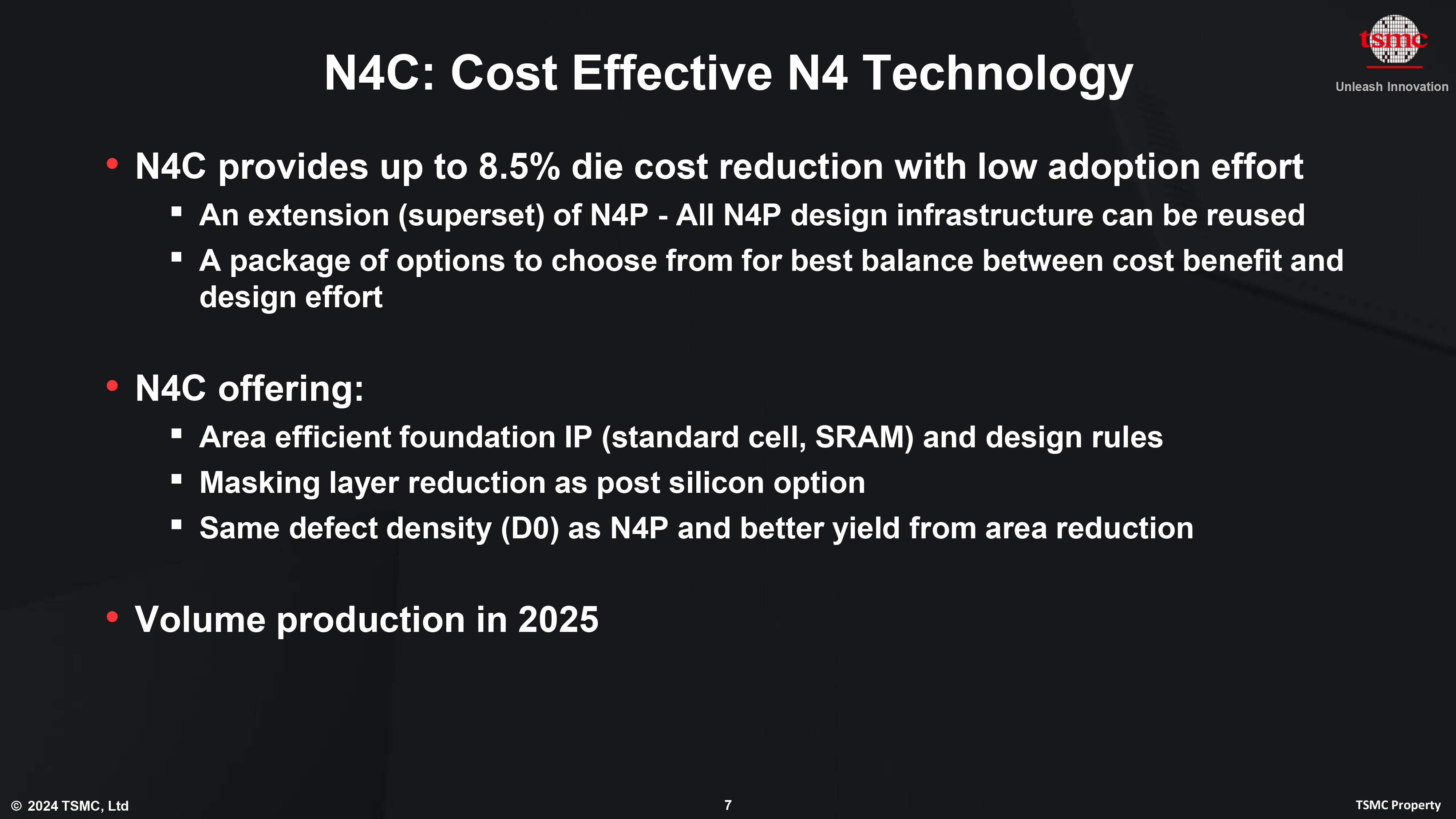

更便宜的N4C工艺

虽然台积电的大部分注意力都集中在其领先的节点上,例如 N3E 和 N2,但未来几年,大量芯片将继续使用更成熟和经过验证的工艺技术来制造。这就是为什么台积电继续完善其现有节点,包括其当前一代 5 纳米级产品。为此,该公司在 2024 年北美技术研讨会上推出了全新优化的 5 纳米级节点:N4C。

台积电的 N4C 工艺属于该公司的 5 纳米级晶圆厂节点系列,是该系列中最先进技术 N4P 的超集。为了进一步降低 5nm 制造成本,台积电正在对 N4C 进行多项更改,包括重新架构其标准单元和 SRAM 单元、更改一些设计规则以及减少掩模层数量。由于这些改进,该公司预计 N4C 将实现更小的芯片尺寸并降低生产复杂性,从而使芯片成本降低高达 8.5%。此外,在与 N4P 相同的晶圆级缺陷密度率的情况下,N4C 由于芯片面积减小,可以提供更高的功能良率。

“因此,我们的 5nm 和 4nm [技术] 还没有结束,”台积电业务开发副总裁 Kevin Zhang表示。“从 N5 到 N4,我们实现了 4% 的光学微缩密度改进,并且我们继续增强晶体管性能。现在我们将 N4C 引入我们的 4 nm 技术产品组合中。N4C 使我们的客户能够通过消除一些掩模并改进标准单元和 SRAM 等原始 IP 设计,以进一步降低总体产品级拥有成本。”

台积电表示,N4C 可以使用与 N4P 相同的设计基础设施,但目前尚不清楚 N5 和 N4P IP 是否可以重新用于基于 N4C 的芯片。同时,台积电表示,它为芯片制造商提供了多种选择,以在成本效益和设计工作之间找到适当的平衡,因此有兴趣采用4纳米级工艺技术的公司很可能会采用N4C。

N4C 的开发正值台积电的许多芯片设计客户准备推出基于该公司最后一代 FinFET 工艺技术 3nm N3 系列的芯片。虽然 N3 有望成为一个成功的系列,但 N3B 的高成本一直是一个问题,而且这一代的特点是性能和晶体管密度回报不断下降。因此,N4C 很可能成为台积电的一个主要的、长期存在的节点,非常适合那些想要坚持使用更具成本效益的 FinFET 节点的客户。

“这是一个非常显着的增强,我们正在与客户合作,基本上是为了从他们的 4 纳米投资中获取更多价值,”张说。

台积电预计将于明年某个时候开始量产 N4C 芯片。随着台积电生产 5 纳米级工艺已近五年,N4C 应该能够在产量和良率方面取得进展。

参考链接:

https://www.anandtech.com/show/21371/tsmc-preps-lower-cost-4nm-n4c-process-for-2025

https://www.anandtech.com/show/21369/tsmcs-16nm-technology-announced-for-late-2026-a16-with-super-power-rail-bspdn

https://www.anandtech.com/show/21370/tsmc-2nm-update-n2-in-2025-n2p-loses-bspdn-nanoflex-optimizations

请先 登录后发表评论 ~