去除铜柱凸块倒装芯片上焊剂的研究

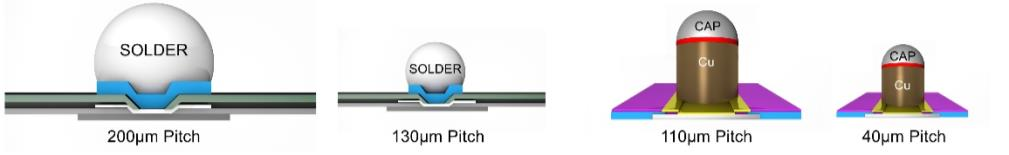

倒装芯片技术是一种将IC芯片器件与沉积在芯片焊盘上的焊点的外部电路互连的方法。倒装芯片技术成本低,封装密度高,能够保持或是提高电路可靠性的同时表现出更佳的工作性能,还能实现高I/O密度,因此在电子行业越来越普遍。然而,有研究表明焊料凸点技术在125μm间距以下有局限性,因为它在制造和组装中面临极大的挑战。随着间距变小,间距的纵向高度及焊点的可靠性都会降低,短路的风险也会增加。

因为这个原因,传统的焊料凸点正在被铜柱技术所取代。作为一级互连,铜柱技术越来越受欢迎。铜柱技术在 80 μm 间距下的应用中是公认有效的,在 40μm 的间距下也是极有可能有效的。除了减小间距外,铜柱还具有其他优势:包括提高电气性能。该技术正变得越来越流行,因为它允许更小的器件,更好地控制支架高度,并减少封装板子层的数量,从而降低成本。采用铜柱技术的设备在单位表面积上具有更多的互连,从而实现更紧凑的间距和更低的支架高度。随着支架高度的降低,助焊剂残留物在回流焊过程中的排气面积减小。因此,迫切需要研究成功去除助焊剂残留物所需的条件,以确保最终产品的功能和可靠性。

助焊剂残留物会以两种不同的方式影响可靠性,尤其是对于底部填充胶工艺。首先,如果焊料凸点、板子或芯片上存在助焊剂残留物薄膜,那么底部填充胶和表面之间的界面附着力会大大降低。一旦底部填充区域受到热冲击、湿度或其他因素的压力,底部填充胶就会从表面分层,并且可以使用声学显微镜检测到间隙。其次,助焊剂会通过物理阻碍底部填充材料的流动而影响可靠性。在凸块之间或芯片与板子之间的间隙中积聚的助焊剂残留物会使间隙缩小到底部填充胶无法流动或边缘流动得更快,从而封装空气并产生空隙。为确保底部填充胶无空隙,必须在所有表面上对底部填充胶进行均匀润湿。如果润湿不均匀,未固化的底部填充胶中的空隙可能会在以后转化为可靠性问题。

本研究涉及在铜柱凸块倒装芯片的清洗工艺中使用直接DI水和新型低浓度碱性清洗剂,挑战能否有效地清除这些组件下方的助焊剂残留物。研究成果可为进一步研究小于15μm的凸块间距和包括2.5D和3D在内的更密集封装提供基准。研究中的清洗度评估方面采用分析/功能测试方法,包括傅里叶变换红外光谱、离子色谱、SEM/EDS、热循环 (TC) 测试、底部填充测试、高温储存寿命 (HTSL) 测试和湿度敏感度 3 级 (MSL-3) 测试。

关键词:倒装芯片,铜柱,细间距, 水清洗,组装,可靠性

引言

自半导体行业出现以来,小型化对新技术和新产品的驱动从未止步。在更小的空间中封装更多的器件对是设计人员来说一直都是挑战。虽然这个挑战看似永无止境,倒装芯片晶圆的出现却迈出了重要一步。此外,由于倒装芯片技术体积小、外形扁平、热性能更好、重量轻且 I/O 密度更高,在电子行业中很快受到青睐。

40 多年前, IBM 和 Delco 开创出初代倒装芯片技术。IBM 的 C4 技术使用蒸发方法将焊料沉积在芯片表面,通常产生 200-250μm 的球形凸起。从那时起,凸块高度、凸块直径和螺距日渐缩小[1]。

制造和组装间距在150μm以下的凸点极具挑战性,所以做到150μm以下容易出现问题。随着焊球间距尺寸的缩小,焊料凸块在细焊球工艺中的局限性显现。凹凸印刷、电镀或凹凸跌落以及凹凸垫尺寸是主要限制因素,器件紧密的布局使得短路的风险也会增加。如今,生产中的模具每个模具多达 25,000 个凸起。预计在未来一两年内,这个数字将增加到每块骰子50-60,000个。

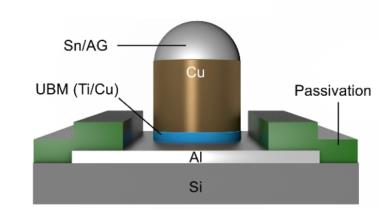

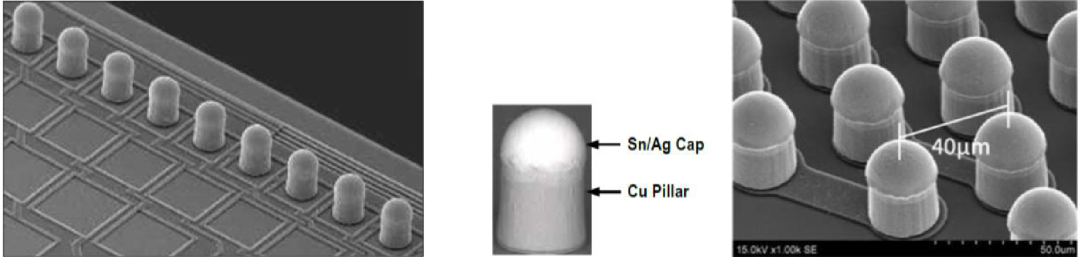

另一种越来越受欢迎的凸块形式是铜柱凸块。这些凸起不是球形的,而是柱子的形式,具有各种形状和大小。最流行的形状是圆柱体的形式。支柱形状容许更大的高度和直径高比,因此即便凸块很高,其间距也可以很紧凑。有时,在柱子顶部形成焊帽,以帮助与配接芯片连接[2]。由于铜柱凸块的圆柱形和不塌陷特性,它们可以很容易地安装在板子上的微型路径里。铜柱是通过TCFC(热压缩倒装芯片)技术将IC芯片“倒装”到半导体封装中的板子上的端子。铜柱是在IC芯片的铝电极焊盘上形成的。

图1:铜柱凸块典型结构

图2:铜柱凸起的SEM图像

凸点高度可以从 5μm 到 100μm 不等,直径可以从 10-20 到 100μm 或更大。现在生产的大多数支柱凸起的高度都大于 20μm。下图是传统的无铅焊料小型化(左)和铜柱倒装芯片小型化(右)的代表性图片。

图3:倒装芯片凸块小型化的典型数据

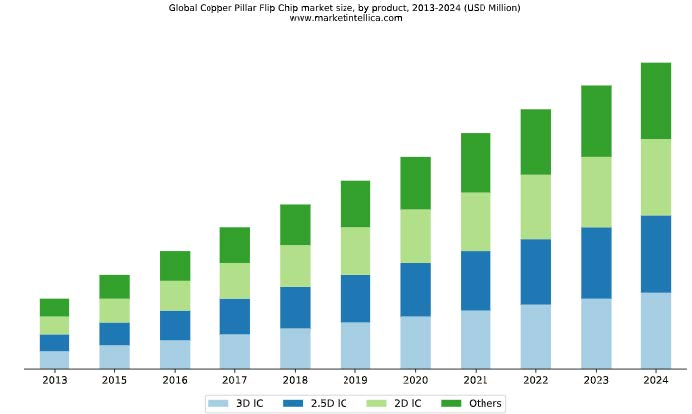

2013年,铜柱技术在倒装芯片中的使用占市场的25%左右,到2020年增加到50%以上,预计到2024年底将占倒装芯片市场的80%左右。铜柱很可能成为未来几年最主要的倒装芯片互连类型。

图4:倒装芯片市场中铜柱技术的历年增长和预测增长t

铜柱技术已被充分证明在低至80μm间距下是有效的,并且对于低至30μm间距也似乎是一种很有前途的方法。除了缩小了间距外,铜柱还具有许多其他优点,包括为高载流能力应用提供卓越的电迁移性能、改进的导热性、简化的UBM 和更高的 I/O 密度。此外,它还可用于低至 40μm 的硅封装器件的极细间距,用于硅通孔(TSV)和片上芯片(CoC)。

这种技术的许多设计都有优势,是下一代倒装芯片互连的方式。同时,它满足当前和未来的 RoHS 要求。对于收发器、嵌入式处理器、电源管理、基带、ASIC和 SOC等应用来说,因为这些应用需要细间距、RoHS/绿色合规性、低成本和电迁移性能的某种组合,所以它是一种出色的互连选择,它的另一个优点是凸起的散热能力,这使它们成为微处理器的良好候选者。

背景

采用铜柱凸块的封装在每个表面积上具有更多的互连,从而实现更紧密的间距和更小的支座间隙。随着支座间隙的减小,助焊剂残留物在回流焊过程中的排气面积更小,导致模具下有更多活性残留物。

助焊剂残留物会以两种方式影响可靠性。首先,在焊料凸点、板子或芯片上,助焊剂残留的薄膜可以显著降低助焊剂与表面之间的界面粘附。一旦底部填充装置受到热冲击、湿度或其他因素的压力,底部填充胶就会从表面分层,并且可以使用声学显微镜检测到间隙。其次,助焊剂还会通过物理阻碍底部填充材料的流动来影响可靠性。助焊剂残留物堆积在凸块之间或芯片与板子之间的间隙中,会将间隙缩小到底部填充胶无法流动或边缘流动速度更快的点,从而封装空气并产生空隙。为确保底部填充胶无空隙,底部填充胶必须在所有表面上均匀润湿。如果润湿不均匀,未固化的底部填充胶中的空隙可能会在以后转变为可靠性问题[5]。

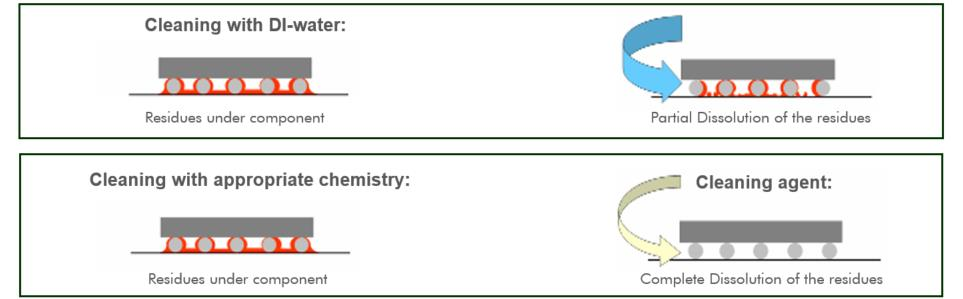

大多数铜柱应用仅使用去离子(DI) 水去除OA助焊剂。然而,大量研究结果表明,水开始达到其清洗极限,使用水基工艺更受青睐[6][7][8]。原因之一是无铅焊料的使用增加要求更高的焊接温度,这会导致更多的烧焦助焊剂出现。当它们开始产生不溶于水的污染物时,这些助焊剂更难去除。仅使用DI水对电路板表面的非离子残留物的溶解能力有限,甚至没有能力。

图5:DI水清洗与化学清洗

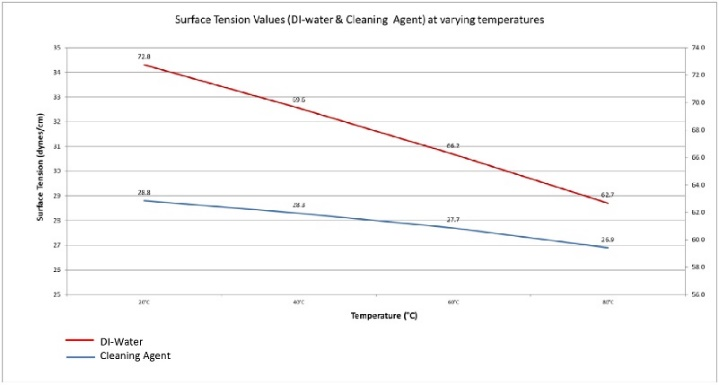

其次,清洗水溶性助焊剂,尤其是组件下的助焊剂,变得越来越困难。换言之,水的表面张力超过70达因/厘米,所以凸块间距小于40μm的情况下,水无法去除助焊剂残留物。

图6:表面张力值

水溶液是一个术语,指水基化合物,例如,应用浓度为15%的DI水。活性物质的浓度水平实际上是次要的。然而,水溶液意味着添加了水性成分。在DI水中稀释的水性清洗剂可显著降低表面张力,通过降低离子污染提供更好的清洗效果,从而提供更高的产品可靠性。这些清洗剂的pH值为中性至弱碱性,其配方中含有缓蚀剂,与铜柱模具上存在的各种金属(Sn、Ag、Cu、Ni、Al等)完全相容。缺乏缓蚀剂很容易侵蚀这些金属,引起电偶腐蚀反应。

本文探讨了分别使用DI水和合适的水性清洗剂去除铜柱凸块倒装芯片上助焊剂的影响。本研究的范围仅限于间距为 150 μm 的铜柱凸块倒装芯片。这项研究将使作者能够确定要想有效去除这些组件下方的助焊剂残留物必须具备的清洗参数和条件,从而确保最终产品的可靠性和功能性。

结果将通过分析测试(IC、SEM/EDS、FTIR)和可靠性测试方法进行验证,包括热循环、高温储存寿命 (HTSL) 和湿度敏感性等级 3 (MSL-3) 测试。

本研究的结果为小于15μm的凸块间距和更致密的封装,包括2.5D和3Ds提供进一步研究的基准。

板子、晶圆、芯片、助焊剂和清洗剂规格

板子规格

本研究中使用的板子是有机材料的,厚度为960μm,具有菊花链功能。芯材为E-679FGR,采用PSR4000-AUS703阻焊剂。焊盘表面采用化学镀镍/沉金 (ENIG)。

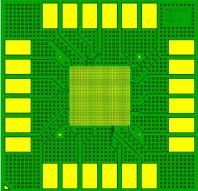

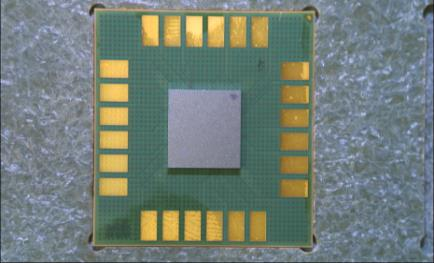

图7:裸板

图8:板子上芯片

晶圆规格

选用8英寸晶圆,其基氧化层由等离子体增强正硅酸四乙酯(PE-TEOS)和TiN/Al-0.5%Cu金属层组成。钝化层是高密度等离子体/等离子体沉积SiN(HDP/P-SiN)的组合,选择的金属化是TiCu/Cu。凸块材料是Cu/Sn-2.5Ag。

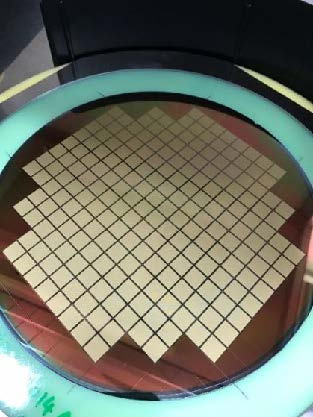

图9:本研究使用的 8 英寸晶圆

芯片规格

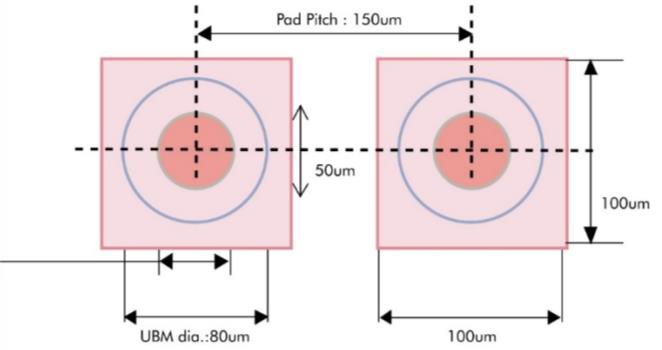

本研究使用了10mm x 10mm菊花链结构的倒装芯片。铜柱设计为150μm凸块间距和30μm铜柱高度。焊盘尺寸100μm平方,凸点直径75μm。总共 3721 个凸块。

• 芯片尺寸:10mm x 10mm

• 焊盘数量:61 x 61 = 3,721 焊盘/芯片

• 焊盘尺寸:100μm平方

• 间距:150μm

• 钝化开度:直径80μm

• 凸点高度:Cu 30μm + SnAg 15μm

• 凸点尺寸:直径 75μm

图10:芯片规格

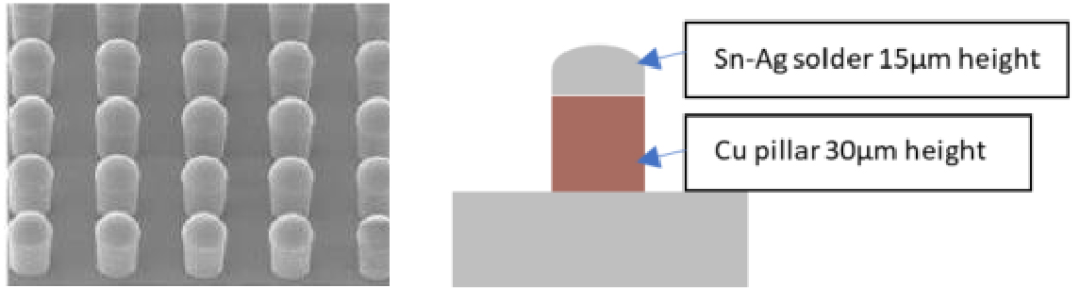

所使用的铜柱几何构造如下图所示。

图11:铜柱几何构造

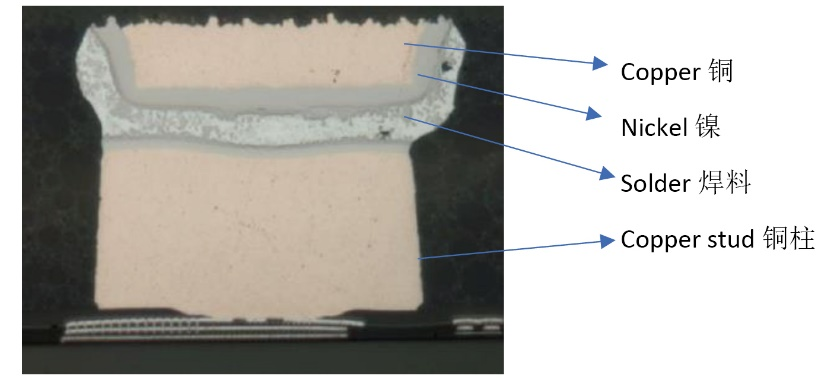

下图展示了铜凸块的横截面。

图12:铜凸块的横截面

助焊剂规格

本研究中使用的助焊剂是一款日本无铅水溶性助焊剂,它是半导体封装中最常用的材料之一,包括应用在铜柱凸块中。化学品供应商反馈,回流和清洗之间的暂存时间为24小时或以上时,代表着最糟糕的情况。

组装工艺

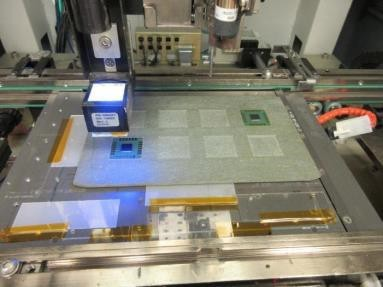

为了获得优化的焊接曲线,组装过程需要适当优化板子上的芯片放置。因此,我们决定与具有组装和执行可靠性测试的能力的环球仪器(Universal Instruments)高级工艺实验室合作。芯片和板子被送往环球仪器高级工艺实验室进行组装。芯片贴装使用的是表面贴装精度极高的自动贴装设备 Universal® Instruments FuzionSC™ 平台。

图13:Universal® Instruments FuzionSC™ 平台

使用线性薄膜涂布机((LTFA)这种机载浸渍工艺施加水溶性助焊剂可最大效率地促进焊料凸块的润湿。LTFA可在助焊剂、焊膏或粘合剂上施加一层薄膜。包装有单个的也有组合的,这样便于在适当的区域涂抹必要数量的材料。它使用厚约38微米的板来制作薄膜。

图14:线性薄膜涂布机(LTFA)

X射线检测

放置后,使用 X 射线进行检查,以确保凸起与垫子正确对齐。在将芯片放置在剩余批次上之前,使用X射线进行首件检查,并做必要的调整使芯片对齐。

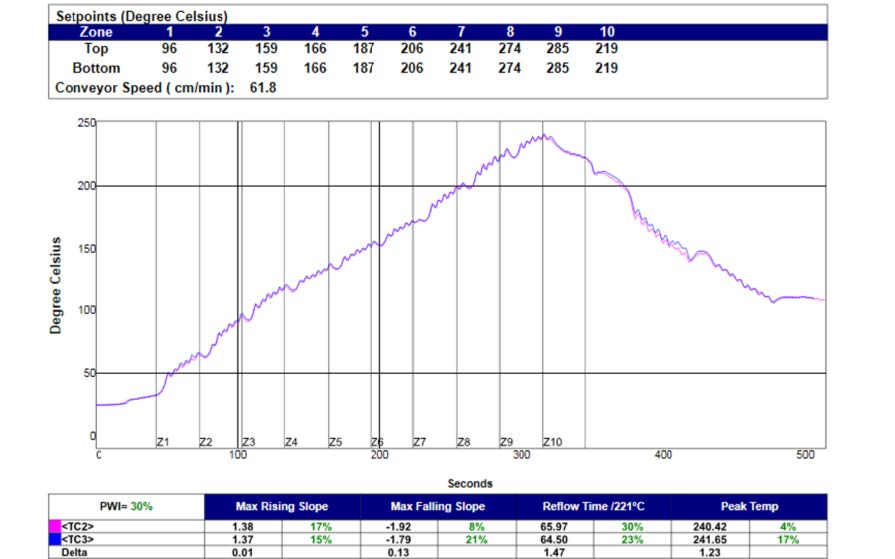

回流焊曲线

选择BTU Pyramax™ 125 10区对流回流焊炉,在氮气(小于200 ppm)下,峰值温度为250°C,使用无铅焊接曲线对封装进行回流。 评估了几个回流焊曲线,直到加热和冷却速率得到充分控制,以获得回流焊后的最佳凸点轮廓,并最大限度地减少回流焊凸块上的应力。由于回流焊过程中的热膨胀系数(CTE)不匹配和板子翘曲,回流焊侧或芯片到凸点界面可能会出现开路凸点。

图15:使用的回流焊曲线

本研究使用的设备

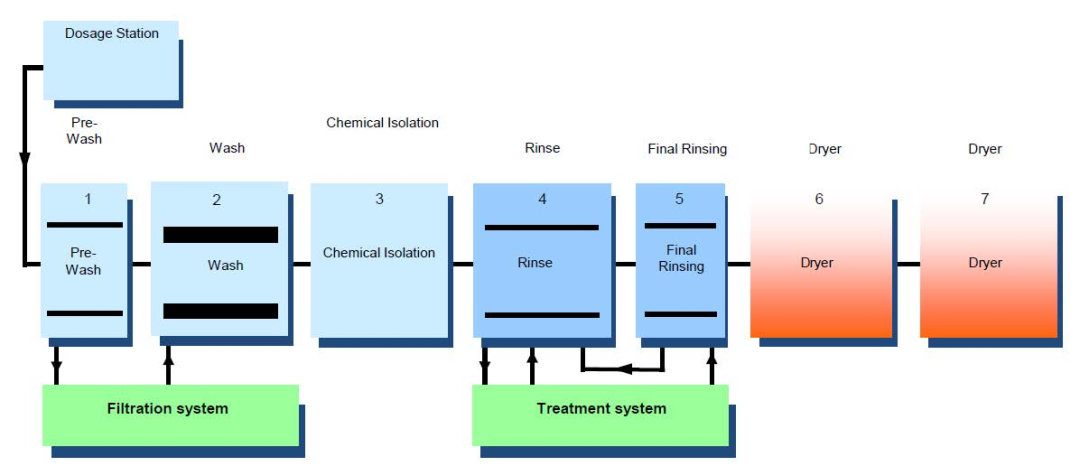

本研究使用了传送带式空气喷淋在线清洗设备。在线清洗系统示意图如下所示。

图16:本研究中使用的输送式喷淋在线清洗设备示意图

研究中使用的清洗剂

100%浓度(10兆欧电阻率)的纯DI水。

一种水基清洗剂,专门用于去除各种封装类型中的无铅水溶性助焊剂,包括堆叠铜柱封装、2.5D/3D TSV 堆栈、BGA 和 SIP,为后续工艺(如底部填充、引线键合和成型)提供最佳表面条件。该清洗剂还与敏感金属具有高度的材料兼容性,建议用于在线和离线空气喷淋清洗工艺。

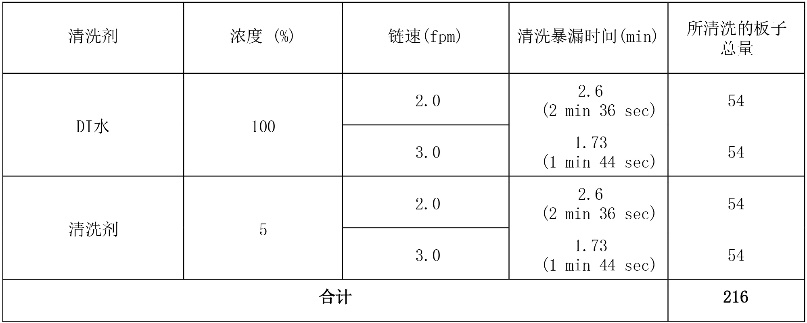

已进行的实验

这项研究总共使用了 216 条样品。

表1:研究中的测试计划

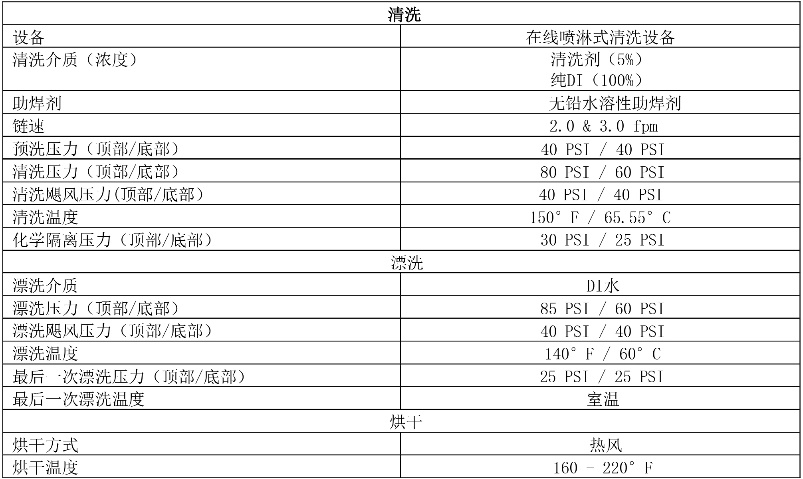

在线清洗设备中使用了以下工艺设置。

表2:在线清洗系统参数设置

清洗试验分为两组,以尽量减少助焊剂分期时间并保持不变。第一批108个基材在 Universal Instruments 进行加工和组装,并在一夜之间运送到清洗剂供应商处,用DI水进行清洗。第二组剩余的108个基材在第二天进行加工和组装,并连夜发货,随后用清洗剂进行清洗。

清洗后,所有基材立即运回环球仪器进行可靠性测试。这包括热循环、高温储存寿命 [HTSL] 和湿度敏感性等级3(MSL-3 测试)。其余清洗的板子进行分析测试(IC、SEM/EDS、FTIR)。

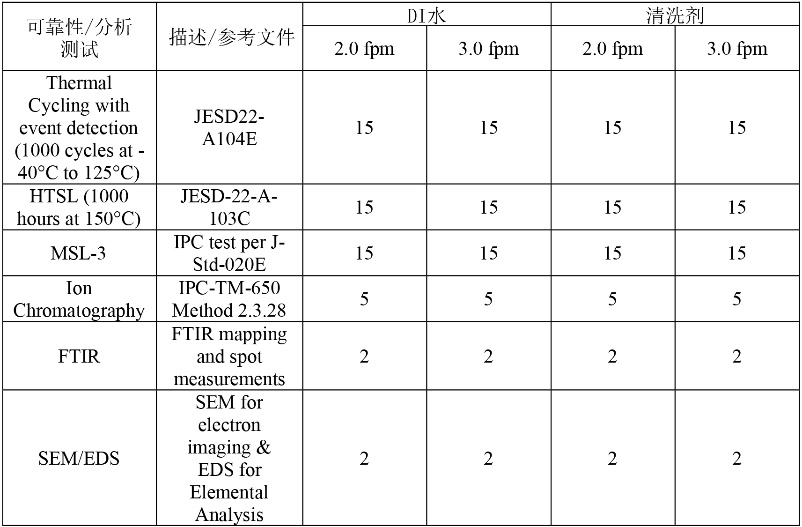

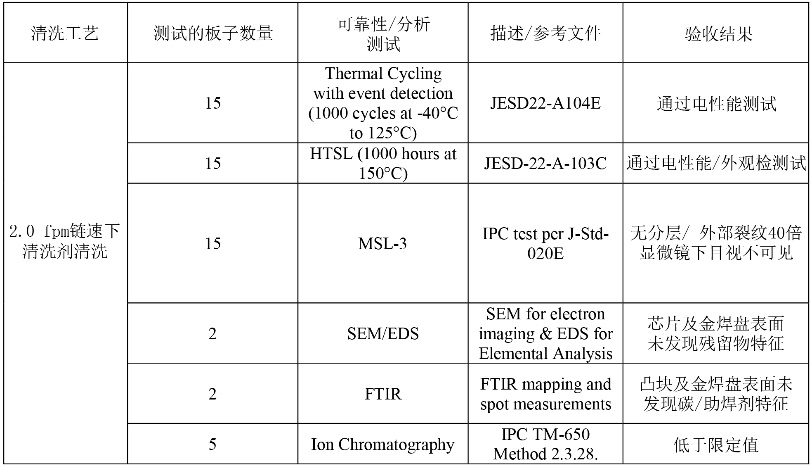

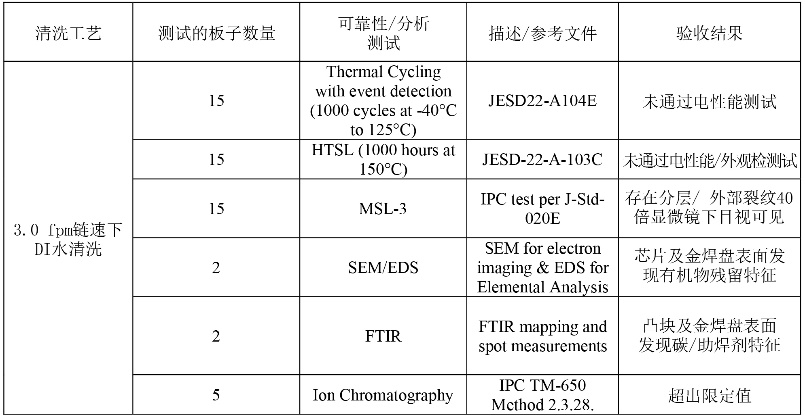

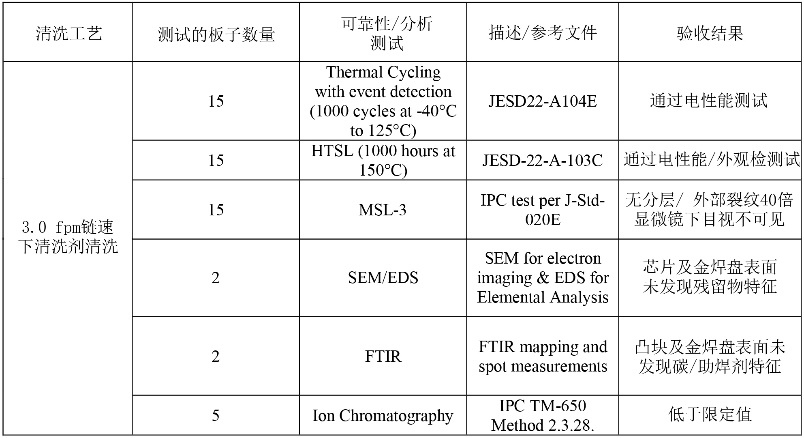

下表详细说明了对使用DI水和清洗剂清洗的基材进行的可靠性/分析测试。

表3:可靠性/分析测试

此外,还对裸板子(共5个)和具有无铅水溶性助焊剂的板子(共5个)进行了离子色谱测试,以确定其清洗度水平和离子种类。

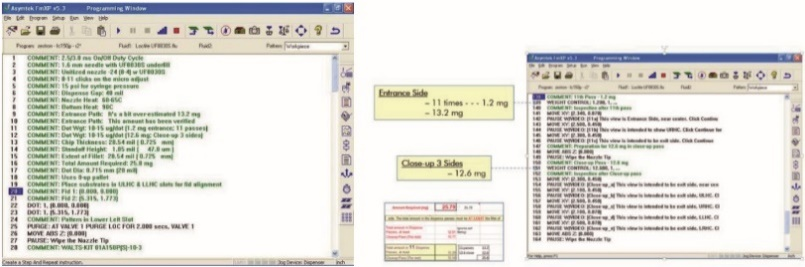

清洗后,使用液态环氧树脂封装剂对板子进行填充不足,该封装剂专为倒装芯片BGA应用中的紧密凸块间距和窄间隙而配制。该过程使用 Asymtek 的 Axiom™ X-1020 点胶系统进行,该系统配置了 Asymtek 的 DJ-9500 点胶喷射阀,用于非接触式喷射点、线和图案的精确体积的流体。

图17:底部填充工艺设置

图18:底部填充工艺设置

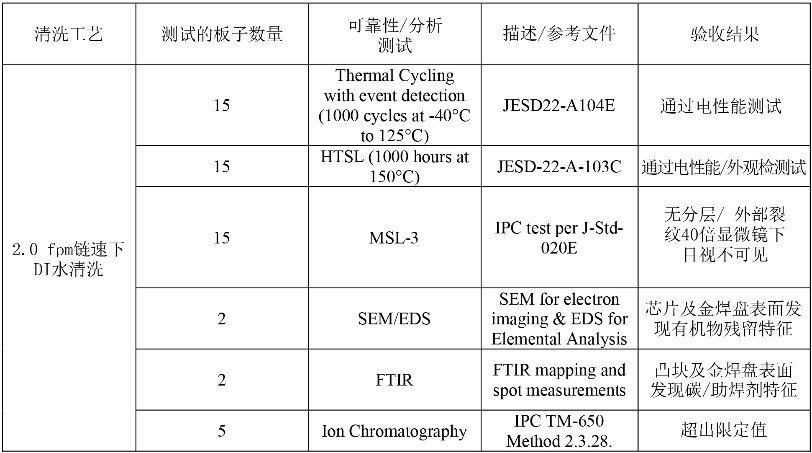

可靠性测试结果

包装可靠性测试的先决条件是水分预处理,以对包装 MSL 等级进行分类,并确保其在浸湿后经受住可靠性测试。将封装在 60°C/30% RH 下进行 MSL-3 预处理 192 小时,然后在 260°C 下进行 3 次回流焊。 信赖性试验结果总结如下:

表4:可靠性测试结果 – 2.0 fpm链速下DI水清洗

表5:可靠性测试结果 – 2.0 fpm链速下清洗剂清洗

表6:可靠性测试结果 – 3.0 fpm链速下DI水清洗

表7:可靠性测试结果 – 3.0 fpm链速下清洗剂清洗

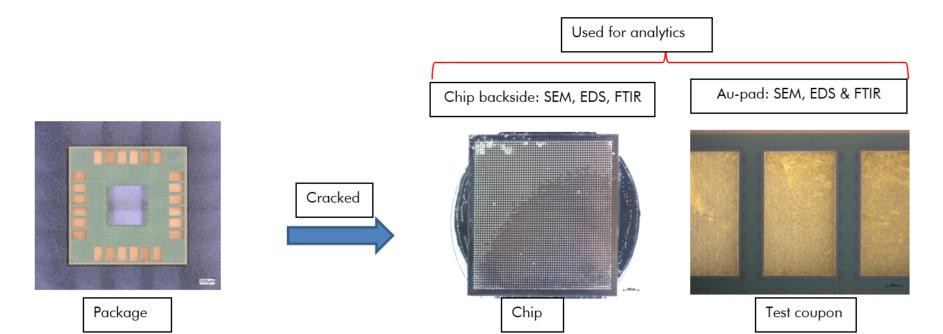

SEM/EDS/FTIR分析

分析的目的是评估芯片组件下的整体清洗度以及Au-pad的表面清洗度。清洗后,将板子断裂,并应用SEM/EDS和FTIR分析芯片和测试板子(Au-pad)。

图19:分析检查前的板子准备

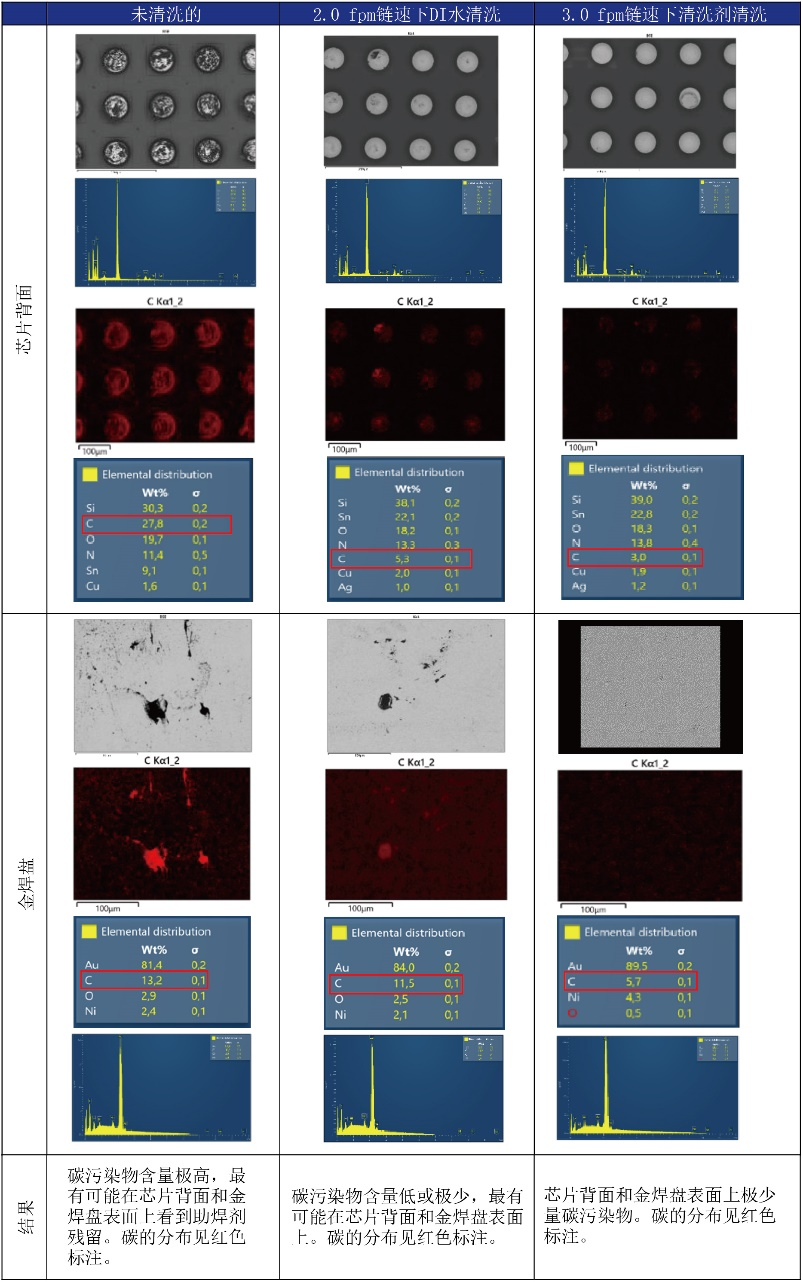

SEM/EDS分析

使用 Zeiss Sigma 300VP 和 Oxford X-maxN 80 进行SEM/EDS分析。全程4.5小时对整个板子表面进行200倍放大倍率扫描,共截取667张照片。这些照片是使用Zeiss SmartStitch软件拼接在一起的。本研究采用了1.5kV的BSE检测。BSE检测通常对有机污染物/残留物(黑色=有机物)的存在非常敏感。它可以指示材料的密度。高密度的材料看起来更亮(例如金属),而密度较低的材料看起来更暗(例如助焊剂残留物等有机物)。

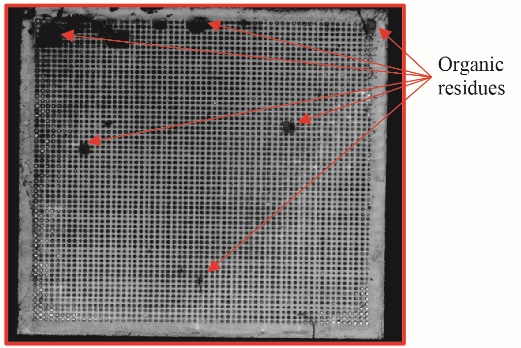

下图是未清洗的铜柱板子(芯片背面)的缝合区域示例。该图像由 300 张图片拼接而成。观察到的深色区域表明存在有机助焊剂残留物

图20:SEM图像下未清洗的铜柱板子上显现有机助焊剂残留

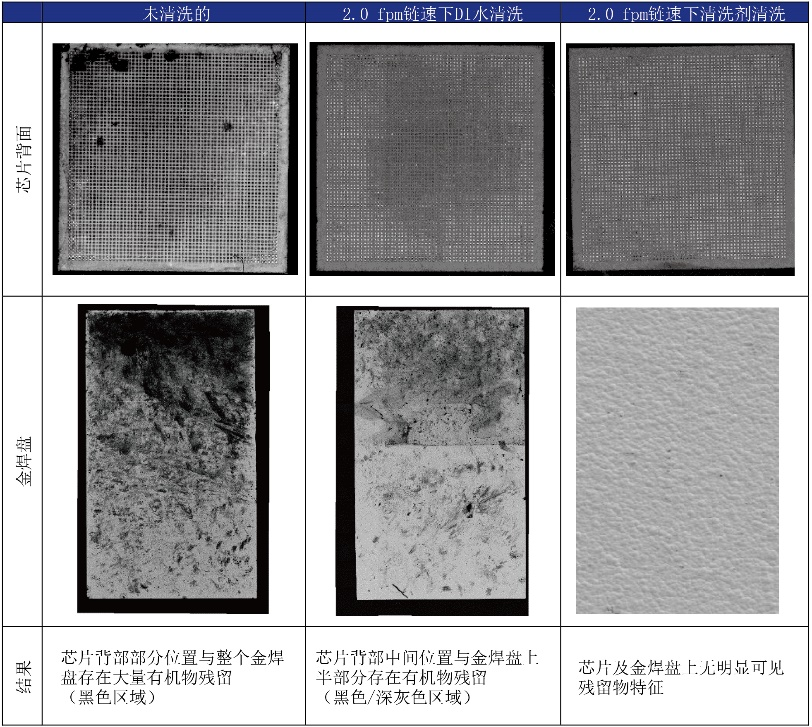

表 8:SEM:未清洗的(左)、2.0 fpm链速下DI水清洗(中)、2.0 fpm链速下清洗剂清洗(右)

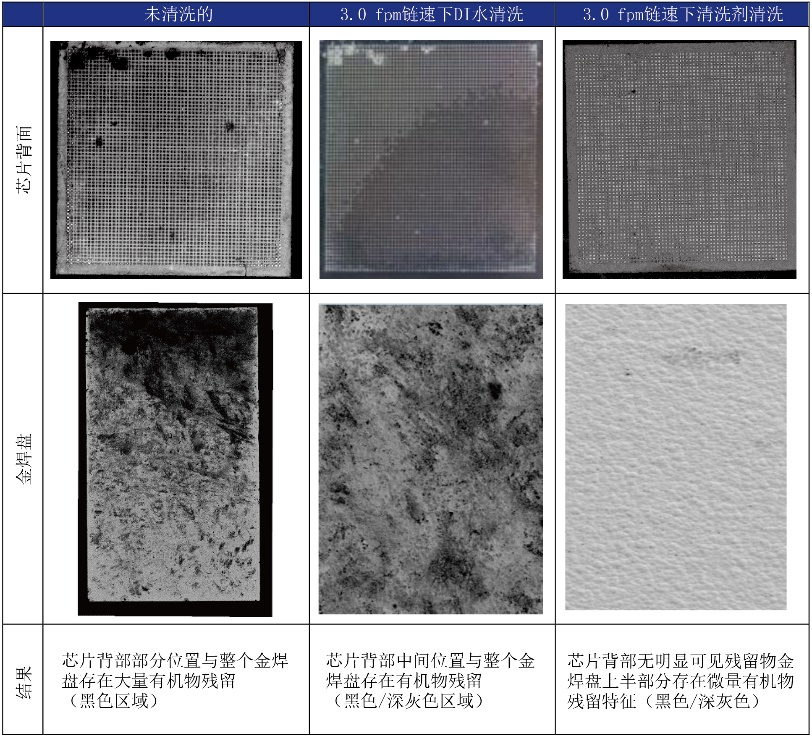

表 9:SEM:未清洗的(左)、3.0 fpm链速下DI水清洗(中)、3.0 fpm链速下清洗剂清洗(右)

表 10:EDS:未清洗的(左)、2.0 fpm链速下DI水清洗(中)、3.0 fpm链速下清洗剂清洗(右)

SEM/EDS 总体结果:

链速2.0 fpm时,用DI水清洗的芯片和Au-pad上都显示存在有机残留物。当链速提高到 3.0 fpm 时,能在芯片和 Au-pad 上观察到大量残留物。使用清洗剂时,2.0 fpm 没有表现出任何残留物,而链速提高到 3.0 fpm 时,Au-pad 上看到非常少量的残留物。总体而言,与“未清洗”基材和用DI水清洗的基材相比,用清洗剂清洗的基材显示出最少的残留物量。

傅里叶变换红外光谱分析

使用布鲁克LUMOS™设备进行FTIR分析。光谱仪配有液氮冷却检测器。测量在ATR(衰减全反射)模式下进行。

图21:FTIR分析

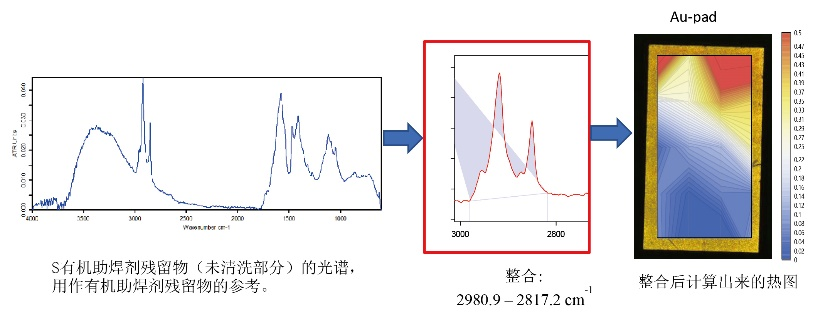

傅里叶变换红外热图生成方法

图22:FTIR红外热图示例

在ATR模式下取20个测量点(每个125x125μm)扫描Au-pad表面。通过整合,确定有机信号在2980.9 – 2817.2 cm-1范围内。将所获得的 20 个点转换为热图。傅里叶变换红外图可以指示碳/通量污染的强度。参照通量谱,红色区域表示有机污染程度高,蓝色区域表示有机污染非常低或为零。对所有光谱进行CO2校正(约2400至2200 cm-1)。

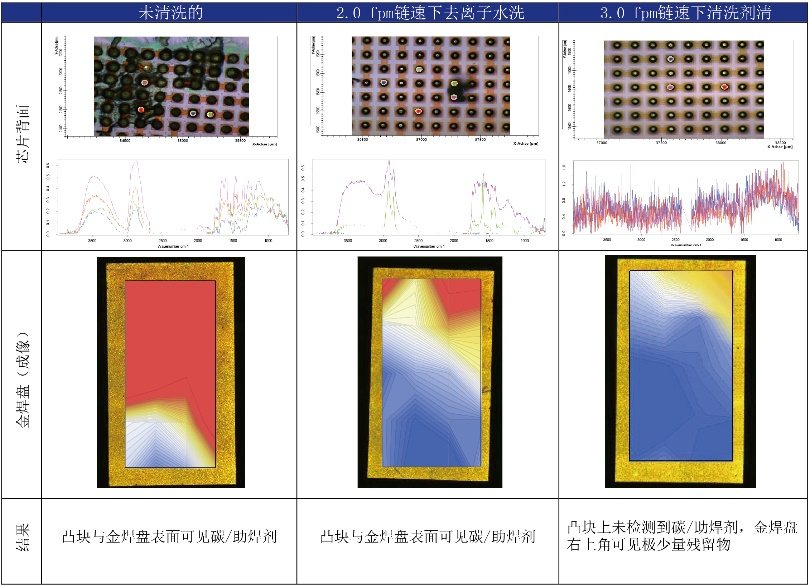

表 11:FTIR 结果:未清洗的(左)、2.0 fpm链速下DI水清洗(中)、3.0 fpm链速下清洗剂清洗(右)

FTIR总体结果:

在2.0fpm链速下,用DI水清洗的基材在凸块和 Au-pad 上都显示存在大量的残留物。在3.0fpm链速下,使用清洗剂清洗的基材在凸起上没有表现出任何碳/通量信号。应该注意的是,在右上角的Au-pad上可以看到非常小的残留物。

总体而言,与用DI水相比,清洗剂所清洗的基材看上去由明显的效果改善,即使在更快的输送带速度下也是如此。

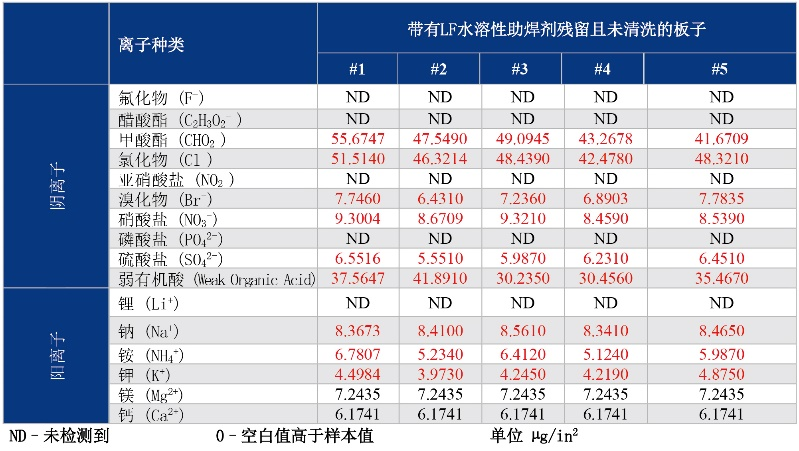

离子色谱结果

所有测试试样均按照IPC TM-650方法2.3.28进行离子色谱分析。IC分析使用10/90 v/v IPA/DI水的萃取溶液。

表 12:IC结果 – 裸板

表 13:IC结果 – 带有LF水溶性助焊剂残留且未清洗的板子

表 14:IC结果 – 2.0 fpm链速下使用DI水清洗的板子

表 15:IC结果 – 3.0 fpm链速下使用DI水清洗的板子

表 16:IC结果 – 2.0 fpm链速下使用清洗剂清洗的板子

表 17:IC结果 – 3.0 fpm链速下使用清洗剂清洗的板子

IC 结果

• 所有通过测试的裸板子上只存在少量离子。

•带有无铅水溶性助焊剂残留物且未清洗的基材显露出大量的阳离子、阴离子和弱有机酸。

• DI水清洗的样本表现出高水平的甲酸盐和氯离子,未通过 IC 测试。2.0 fpm链速时,即使4号板子 通过了 IC 测试,甲酸盐离子的值非常接近合格线。3.0 fpm链速时,观察到乙酸盐、甲酸盐和氯离子出现显著失效。

• 用清洗剂清洗的基材通过了 2.0 和 3.0 fpm链速时的 IC 测试,大多数离子物质低于合格线。

结论

这项对比研究证实,使用DI水难以持续有效地清洗低底部间隙内的焊剂残留物,尤其是在清洗凸块间距为 150μm 且铜柱高度为 30μm 的铜柱封装时。

使用DI水所清洗的板子在3.0 fpm时无法通过热循环测试,HTSL和MSL-3测试。此外,在开展SEM/EDS/FTIR分析时,能看到芯片背面和金焊盘上存在碳类残留物。离子色谱测试时显示离子种类水平很高。

相比之下,使用过清洗剂的板子经过了热循环测试,HTSL和MSL-3 测试。清洗剂在芯片组件下的封装器件以及金焊盘上都表现出更好的清洗性能。在开展SEM/EDS/FTIR分析时,仅可见非常少量残留物。离子色谱测试也显示离子种类水平非常低。

整个研究发现,相比于慢链速2.0 fpm下用DI水洗,使用低浓度 (5%) 的清洗剂能够在更快的链速 (3.0 fpm) 下完全去除无铅水溶性助焊剂残留物,所以使用清洗剂能够将产量提高 50%。

值得注意的是,铜柱倒装芯片板子是在组装和焊接过程后 24 小时才进行的清洗。一般来说,建议尽快清洗水溶性粘性助焊剂(最好在焊接后1小时内)。

展望

本研究的结果将用作基准,重点关注低至 40μm 的硅封装器件上的极细间距,以及包括涉及 TSV 的 2.5D 和 3D 在内的更高密度封装。此外,未来的研究将重点关注不同的喷涂技术,以及洗涤温度和焊接条件对这些封装的影响,包括功耗。

致谢

作者要感谢 O.K. Wack Chemie GmbH 博士的研发团队对本研究的持续指导。作者要感谢我们合作伙伴公司的个人,他们帮助设计了先进封装并开展了可靠性测试。

请先 登录后发表评论 ~